Technologie

Zusammenspiel ist gefragt

Beim Testen von bestückten Leiterplatten, auch Flachbaugruppen genannt, spielen mehrere Komponenten zusammen, die sich grob in drei Bereiche einteilen lassen können:

Die Kontaktiereinrichtung

(Adapter)

Die Tester-Hardware

Das Testprogramm

Das Testprogramm wird für jede Baugruppe

individuell erstellt

In Circuit Test (ICT)

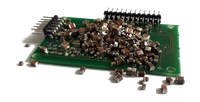

Beim In-Circuit-Test wird die bestückte Leiterplatte auf Bestückungsfehler getestet.

Durch spezielle Technologien (Guarding) lässt sich dabei der Einfluss umliegender Bauelemente eliminieren. So lassen sich in vielen Fällen Testabdeckungen >90% erreichen.

Das Prüfspektrum des ICT umfasst:

- Kurzschlüsse, z.B. Lötbrücken)

- Unterbrechungen

- Widerstände, Kapazitäten, Induktivitäten

- Dioden (auch Verpolungs-Erkennung), Transistoren

- Digitale Logik

- Analoge ICs (OPV, Komparatoren, Linearregler) und vieles mehr

In-System-Programming (ISP)

Bei der In-System Programmierung gibt es verschiedene Ansätze, die Auswahl erfolgt entweder durch die zu programmierenden Devices oder Kundenvorgabe:

- Programmierung über Debug- oder Programmierschnittstellen, direkt über die Tester-Hardware

- Nutzung von Zusatzhardware für Beschleunigung und Parallelisierung

- Einbindung herstellerspezifischer Programmiergeräte

- Einbindung universeller Programmiergeräte

- Programmierung über JTAG durch Einbindung von Hard- und Software der Firma Göpel

Je nach zu programmierenden Devices lassen sich mit den beiden erst genannten Methoden bis zu 128 identische Devices gleichzeitig programmieren

(Nutzen-Programmierung). Dabei ist es auch möglich, variable Daten wie z.B. individuelle Seriennummern zu schreiben.

Boundary Scan Test (BST)

Bei komplexen Bauelementen wie Mikrocontollern lassen sich selbst Tests auf Unterbrechungen mit Methoden des In-Ciruit-Test nur sehr eingeschränkt realisieren.

Zudem entfallen häufig aus Platz oder EMV-Gründen notwendige Testpunkte.

Der Boundary Scan Test (BST) wurde 1990 unter IEEE 1149.1 standardisiert. Mit dem Boundary-Scan können elektrische Tests von bestückten Leiterplatten durchgeführt werden. Boundary-Scan-fähige Chips haben neben der Kernlogik eine zusätzliche Logik, die Boundary-Scan-Zelle, mit einem Test Access Port (TAP).

Der physikalische Zugriff erfolgt beim Boundary-Scan über vier Verbindungsleitungen.

Das Prüfspektrum des BST umfasst:

- Kurzschlüsse, z.B. Lötbrücken)

- Unterbrechungen z.B. bei Jumpern

- Digitale Logik

Active Scan Test (AST)

Der Bauteiletest mit Active-Scan-Test ist in der Funktion vergleichbar dem Boundary Scan Test (BST) nach IEEE 1149.1. Der AST kann bei Mikrocontrollern eingesetzt werden, welche über keine interne BST Logik verfügen.

Beim AST kommen, je nach Device, verschiedene Technologien zum Einsatz:

- Direktzugriff über Debug-Schnittstellen (z.B. BDM, SWD)

- Abarbeitung von Testroutinen im RAM

- Abarbeitung von Testroutinen im Flash

Functional Test (FCT)

Beim Functional-Test können einzelne Funktionen der Baugruppe getestet werden. Dazu gehören zum Beispiel Stromversorgung (Schaltregler) und Kommunikationsbusse (z.B. RS232, LIN und CAN).

Neben dem Test auf Funktion lassen sich auch noch weitere Funktionen realisieren:

- Auslesen von Software-Versionen

- Lesen und Schreiben von Parametern

- Serialisierung, Schreiben von Seriennummern

Adapter (Kontaktiervorrichtung)

Für die verschiedenen Testverfahren wird die bestückte Leiterplatte auf speziellen Testpunkten mittels federnder Nadeln kontaktiert.

Die dafür erforderliche Kraft wird auf Einzeltestplätzen per Vakuum und bei Integration in Produktionslinien mechanisch erzeugt. Die Kontaktierung kann ein- oder auch zweiseitig erfolgen.

Demovideo - so funktioniert ICT